**State Machine Library - User's Manual**

# Altair® Twin Activate® 2024.1

# **Contents**

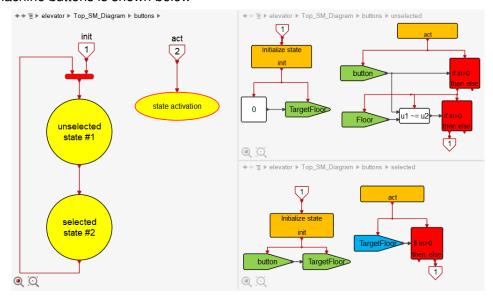

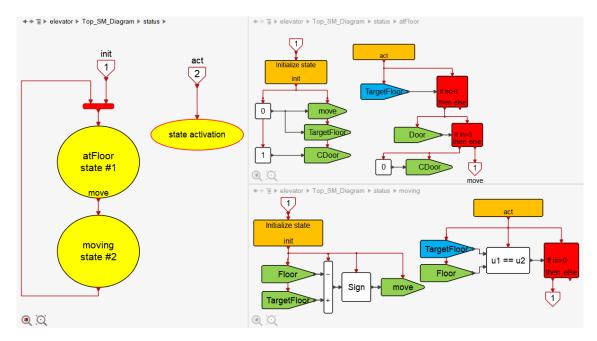

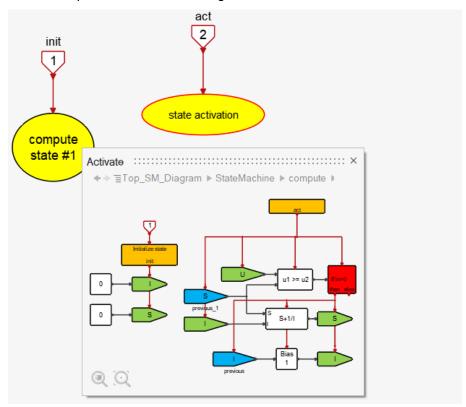

| Pi | reface                                                                                                                                                                                             | 5                                |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| ı  | Discrete-time state machines                                                                                                                                                                       | 7                                |

| 1  | Introduction  1.1 Block diagrams vs State machines                                                                                                                                                 |                                  |

| 2  | State Machine Library (ASM)  2.1 ASM library palette                                                                                                                                               |                                  |

| 3  | How does it work  3.1 State machine                                                                                                                                                                | 27<br>27<br>29<br>29<br>31<br>34 |

| 4  | Code Generation 4.1 Creating a new block                                                                                                                                                           |                                  |

| 5  | Pitfalls and common mistakes   5.1 Algebraic loop errors   5.2 Infinite loops   5.3 Unintended block activations inside inactive states   5.4 Improper state exits   5.5 Debug mode error messages | 54<br>55<br>55                   |

|    | Example: Vehicle with adaptvie cruise control and automatic transmission  6.1 Adaptive cruise control (ACC)                                                                                        | 62<br>63                         |

| 3  | ASM library Altair Twin Activate 2024                                                                                                                                                              | .1                               |

| 7  | Mair  | the state of the s | 65 |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

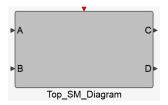

|    | 7.1   | Top_SM_Diagram block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65 |

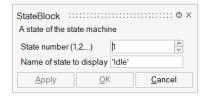

|    | 7.2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66 |

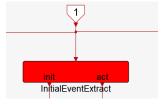

|    | 7.3   | InitialEventExtract block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67 |

|    | 7.4   | Initialize and Action blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

|    | 7.5   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67 |

|    | 7.6   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69 |

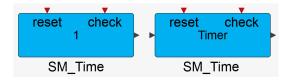

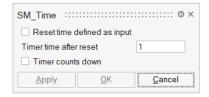

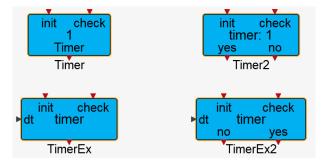

|    | 7.7   | Time and Timer blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69 |

|    | 7.8   | Counter block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70 |

|    | 7.9   | StateNumber block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70 |

|    | 7.10  | Animate block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71 |

| II | Cor   | ntinuous-time state machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73 |

| 8  | Intro | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75 |

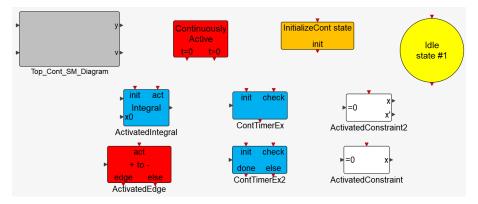

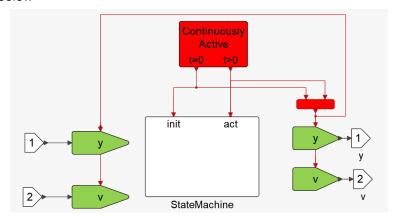

| 9  | 9.1   | cary blocks for continuous-time state machines  ContinuouslyActive sub-palette                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 10 |       | or or types or communication and control materials.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81 |

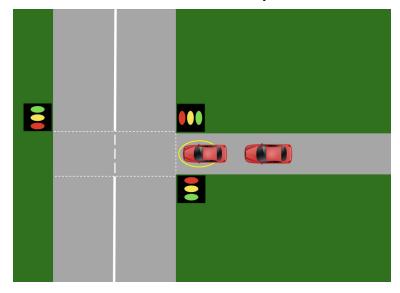

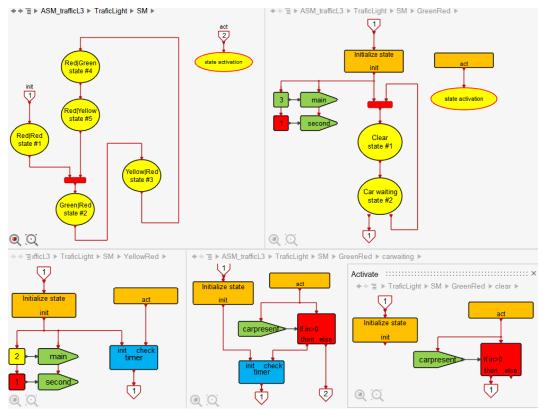

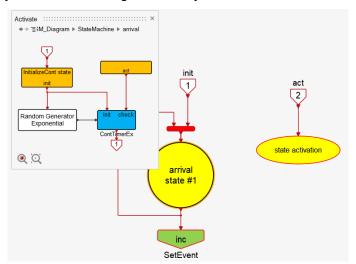

|    | 10.1  | Modeling asynchronous events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81 |

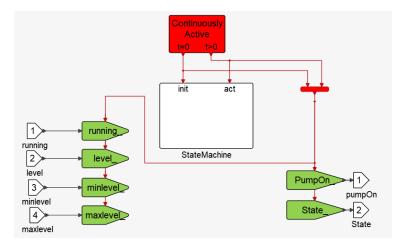

|    | 10.2  | 2 Always-active state machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83 |

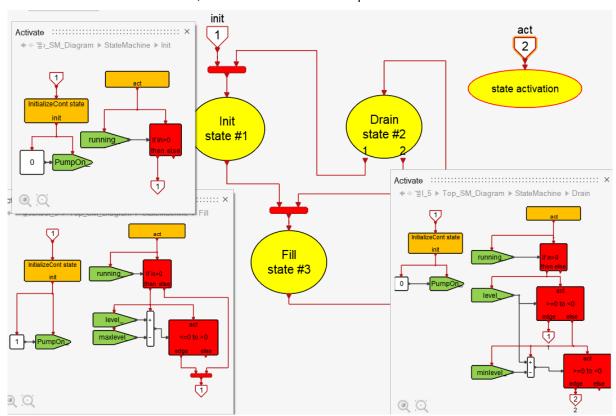

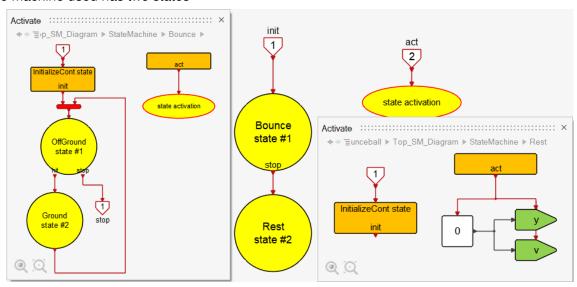

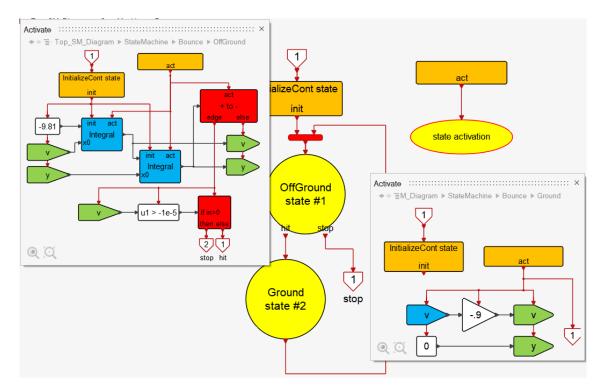

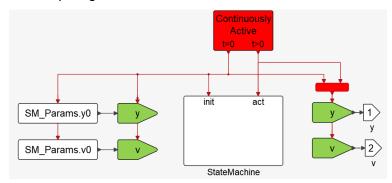

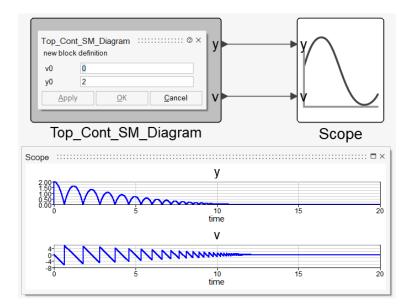

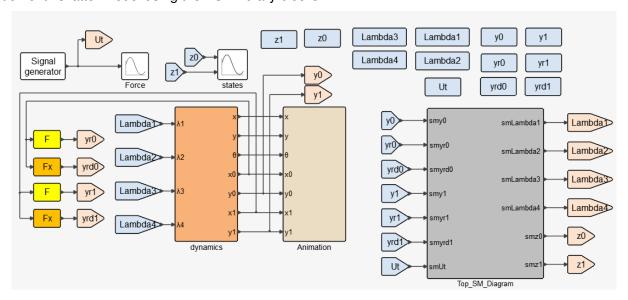

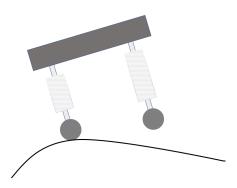

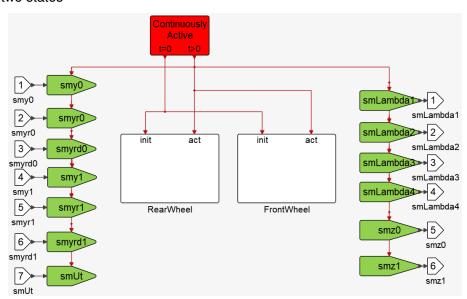

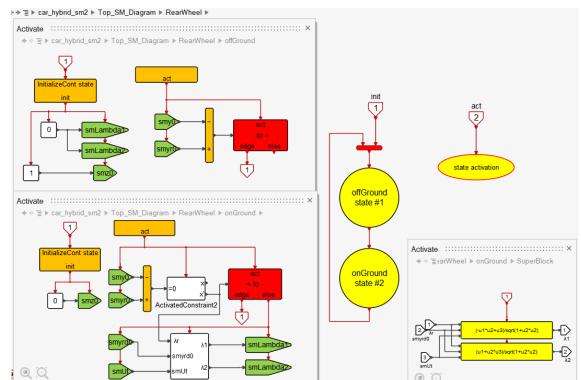

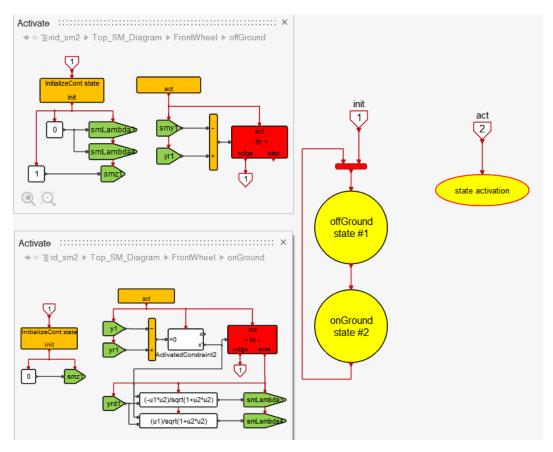

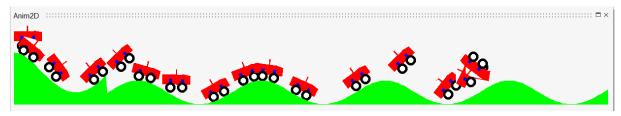

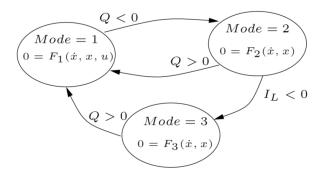

|    | 10.3  | B Hybrid systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 84 |

| 11 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91 |

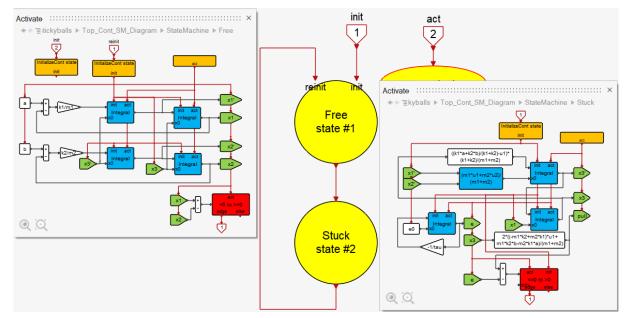

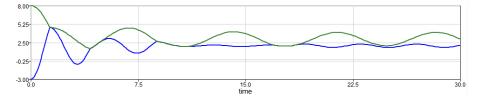

|    |       | Sticky masses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

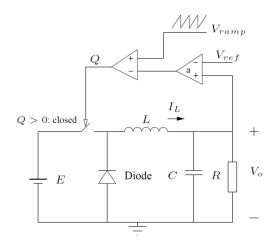

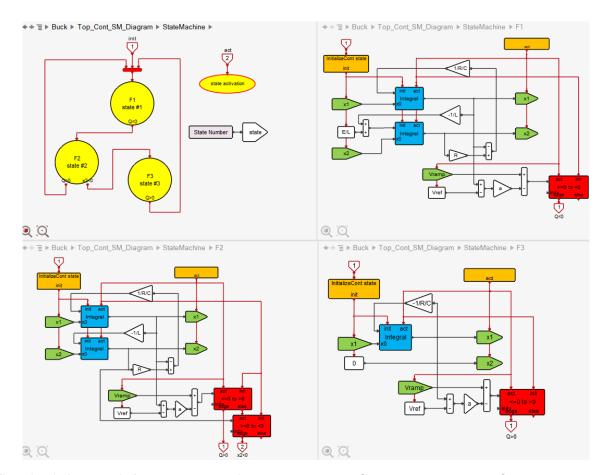

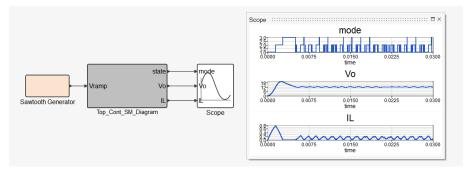

|    |       | 2 DC/DC Buck Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 94 |

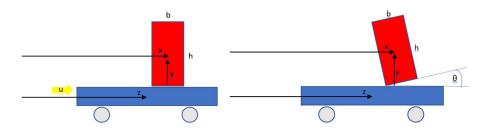

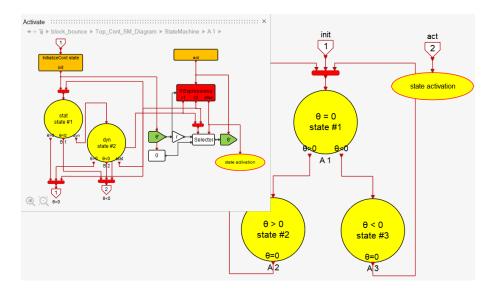

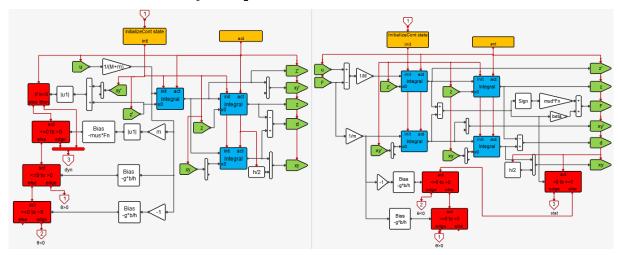

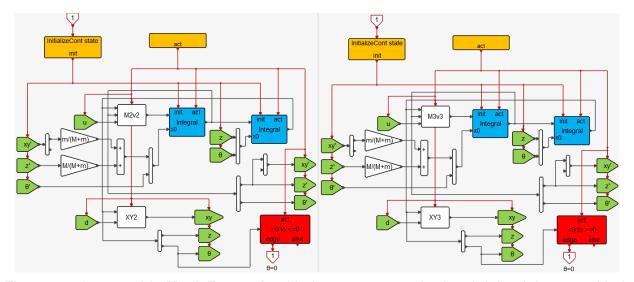

|    | 11.4  | Block on a cart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 96 |

| 12 |       | ttinuous-time specific blocks 1 InitializeCont block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 03 |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    |       | Proproperties of the Control of the  |    |

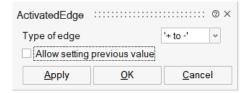

|    |       | ActivatedEage block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|    |       | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

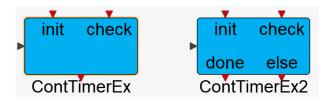

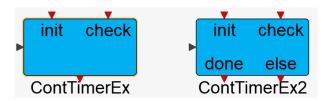

|    |       | 5 Timer blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|    | 12.0  | ) ounguanu nioung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UU |

Altair Twin Activate 2024.1 ASM library 4

### **Preface**

**Altair® Twin Activate®** is a modeling and simulation tools for dynamical systems. It provides a graphical block-diagram editor for constructing models using blocks. State machines [8, 10] provide a different approach to modeling synamical systems. Basic **Twin Activate** does not provide facilities for constructing state machines within models. **Twin Activate** semantics however is particularly well adapted for such constructions [1, 3].

The **State Machine Library** provides a set of blocks for constructing dynamical system components based on the paradigm of state machines. This user's manual provides information about the type of state machines that can be constructed using this library, and illustrates the use of its blocks through examples.

The **State Machine Library** provides one way of constructing state machines; it is not the only way. It provides a State machine formalism very much in the spirit of **Twin Activate**. It is a simple, yet powerful formalism, offering many features available in other formalisms, such as different variants of Statecharts, Stateflow [11], Scade [7], SyncCharts [4], UML State Machine [12], but it is not fully compatible with any of them.

The manual contains two parts. Part I is dedicated to discrete-time synchronous state machines, used in particular for modeling embedded controllers. Part II presents an extension to the continuous-time case, used for modeling asynchronous state machines and hybrid systems.

The example models used for illustration in this manual are available as demo models of the library.

# Part I

# **Discrete-time state machines**

# **Chapter 1**

### Introduction

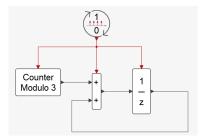

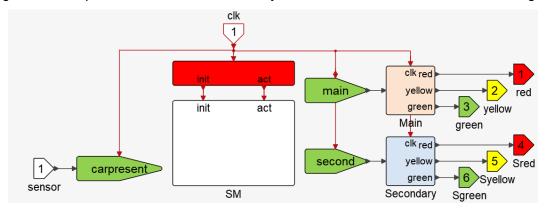

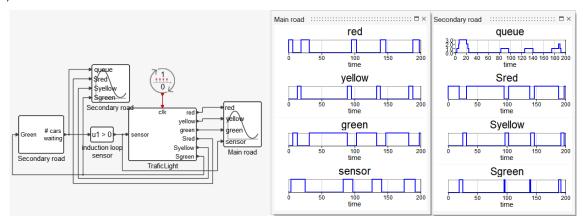

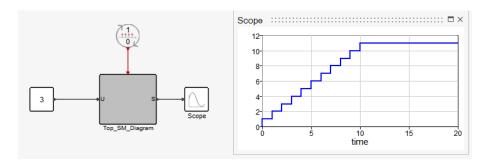

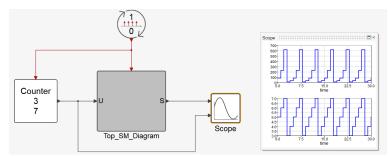

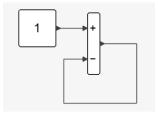

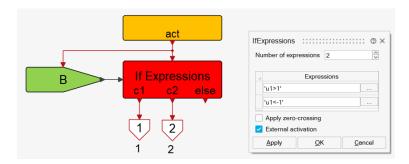

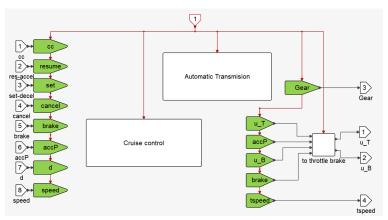

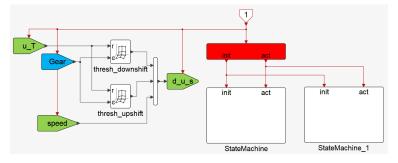

**Twin Activate** diagrams are based on interconnected components, called blocks, performing mathematical operations, and exchanging data. In simple cases, all the blocks are activated by the same clock at the same times (synchronously) and the order in which the block operations are performed is determined by the **Twin Activate** compiler. For example, in the following model

the Counter, the Sum and the Delay blocks are activated synchronously every unit of time<sup>2</sup>. The state of this system/model is constituted of the internal states of the blocks, in particular the internal states of the Counter and the Delay blocks. The model state is not apparent on the diagram but hidden inside its individual constituents.

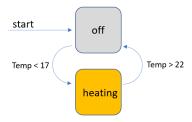

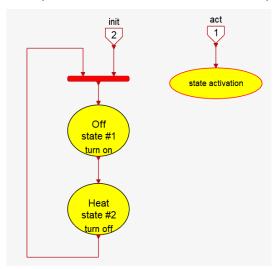

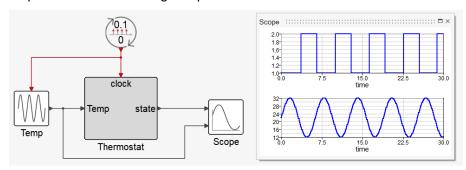

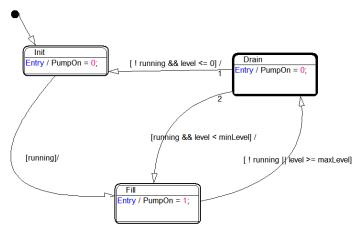

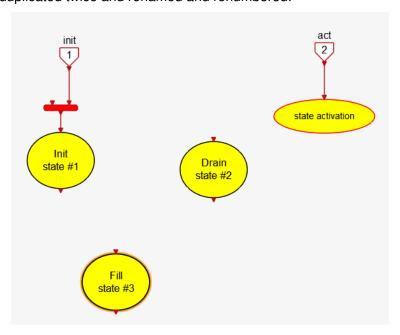

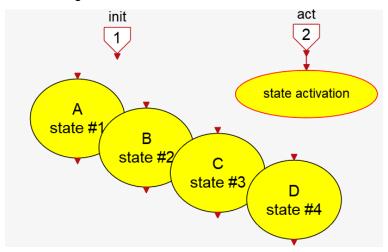

A state machine model is a different way of modeling dynamical systems. In a state machine diagram, only one component is active at any time, and it represents the complete state of the model. There are no hidden states inside the component. For example, the following diagram represents a state machine modeling a simple thermostat<sup>3</sup>

where the system can be in one and only one state at a time (system is in off mode or in heating

<sup>&</sup>lt;sup>2</sup>Since the Delay block does not require its input value to produce its output value, it can update its output before the Sum block does, so the order of output update operations could be either Counter, Delay followed by Sum, or, Delay, Counter followed by Sum. The block states are then updated in any order.

<sup>&</sup>lt;sup>3</sup>The temperatures are expressed in centigrade in this model.

mode). This representation of states is sometimes referred to as diagrammed states. The block diagrams and the state machines represent two orthogonal and complementary approaches to modeling dynamical systems. Even when they are both available in a modeling environment and can be used in the creation of the same model, they are often provided as separate, communicating, tools each with its own semantics. This can create ambiguity in the behavior of the overall model and imposes many limitations.

The state machine implementation presented here is fully based on **Twin Activate** synchronous reactive semantics. This allows for very intimate interactions between the block diagram and state machine components of the model without any risk of ambiguity. Blocks in block diagrams may contain state machines, and states in state machines, block diagrams. The overall system being implemented in the same environment, model compilation, both for simulation and code generation purposes, is done by a single compiler.

### 1.1 Block diagrams vs State machines

In reality, the distinction between block diagram modeling and state machine modeling is not so categorical. Many block diagram formalisms accept blocks running on different clocks in the same model (with different interaction constraints) and there exist different flavors of state machine formalisms where multiple components can be active simultaneously by allowing concurrent (parallel, orthogonal) and hierarchical constructions, with support for extended (not diagrammed) states. These extensions bring closer the two approaches. The State machine formalism presented here is an attempt to fill this gap even further and even completely close it.

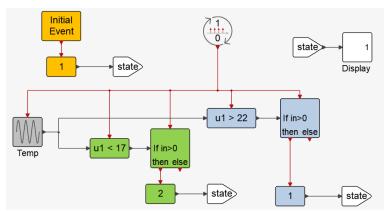

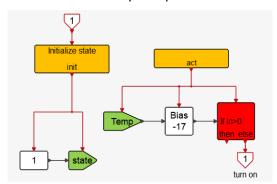

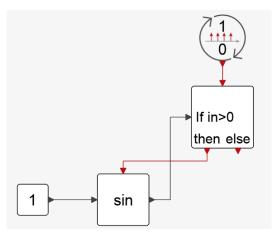

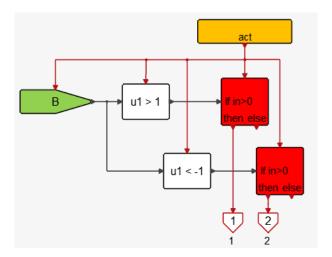

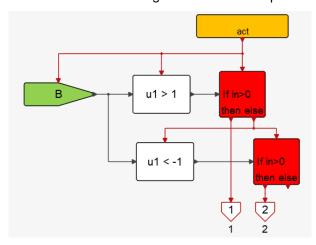

**Twin Activate** provides direct manipulation of "activation signals" (clocks) based on the semantics of synchronous languages. This makes it particularly amenable to use for constructing the dynamics of discrete finite state machines. Consider for example the simple thermostat with two states presented above and the following implementation of it in **Twin Activate**.

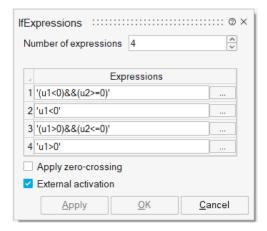

The state signal represents the state taking values 1 and 2 corresponding, respectively, to the Off and the Heating states of the state machine. This state is initially set to 1 (Off) and then it is updated by the **Constant** blocks, which are activated when the temperature falls below 17 or goes above 22. The explicit manipulation of activation signals through condition blocks (in particular, the **IfThenElse** block<sup>1</sup> here) is used to activate the two **Constant** blocks at different instants of times to change the state.

<sup>&</sup>lt;sup>1</sup>IfThenElse block is strictly speaking not a block. Along with **SwitchCase**, they are language constructs presented as blocks, but their output events are not generated by them; they are redirections of their input events, so, the input and output events are synchronous. They can be compared to if-then-else and switch constructs of most programming language.

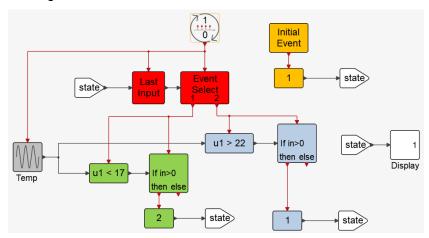

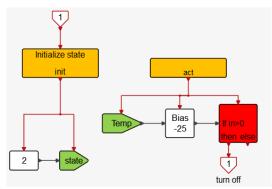

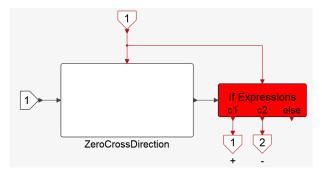

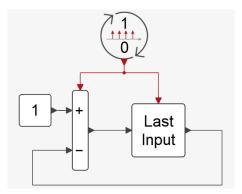

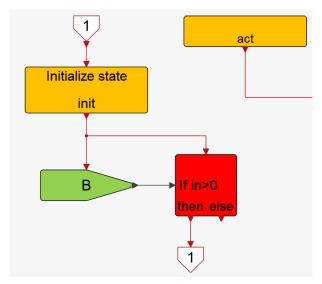

This model remains relatively simple because the underlying state machine transitions can be made solely dependable on the input (note that this is done by accepting extra useless operations; for example, if the temperature is below 17, the state is systematically set to 1 regardless of whether it is already 1, or not). This kind of construction however is not possible in general. The construction of an **Twin Activate** model to allow the dependency of the new state on the previous state is possible but can be complicated. For example, an alternative realization for the same state machine, not producing the extra activations, is given below.

The activations of the **Constant** blocks now depend both on the previous value of the state and the input. Based on the value of the previous state, only the relevant test of the input temperature is performed. So, for example if the state is 1, the input (temperature) is only tested against 17 and changed if needed; it is not tested against 22. It turns out that this way of storing the previous value of the state and using it with the **SwitchCase** (Even Select) block to activate the part of the model corresponding to that state can systematically be used in the construction of models for any state machine.

This example illustrates three points: the construction of state machine models in **Twin Activate** from scratch can become very complex and users should not be expected to do it without assistance; all that is needed to construct them is already available in **Twin Activate** and the construction can be systematic; and finally, the resulting model does not look like a state machine. These observations have been the motivation and starting point for the development of the **State Machine Library**.

### 1.2 Discrete-time assumption

The state machines considered here are activated by external events. All state transitions and activations occur by these events, and all the signals used in the state machine may only be updated synchronously at these event times. The top diagram encapsulating the state machines realizes a discrete-time **Twin Activate** block (an Atomic super block to be exact), whose activations provide the external events activating the state machines. So, the block inputs are read, processed, and the outputs are generated when the block is activated. The processing may include multiple iterations of the same event in the state machines inside the block, but the iterations are transparent from the outside.

The block activation in the model is often done by a periodic clock (**SampleCLK** block) but it can be done by any series of events. For example, the block can be activated only under certain conditions, such as only when the value of an input to the block is changed.

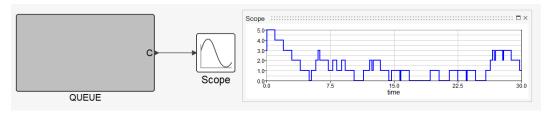

Future extensions of the ASM library will provide blocks to support asynchronous state machines and hybrid systems. For asynchronous state machines, the activation times are not imposed by external events; events can be internally generated at any time. Queuing processes, for example the Poisson process, can be generated by such state machines. The resulting blocks would be "always active". If in addition the state machines support continuous-time states, they can be used to model hybrid systems.

Asynchronous processes and hybrid systems can already be modeled in **Twin Activate**, and the demos present several examples. But these constructions are not always based on a state machine methodology. A specialized library would provide a systematic state machine approach for the construction of such models.

Altair Twin Activate 2024.1 ASM library 12

# **Chapter 2**

# **State Machine Library (ASM)**

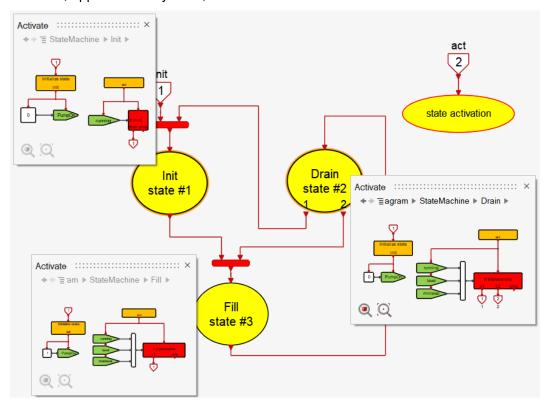

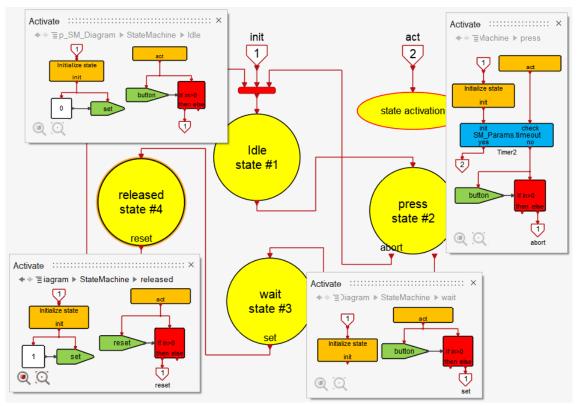

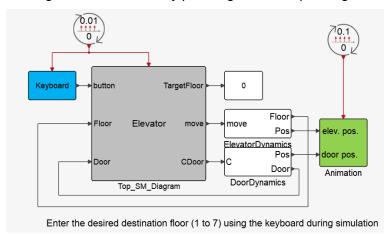

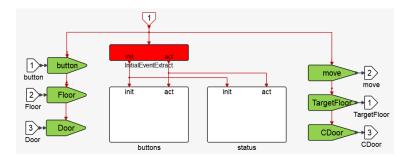

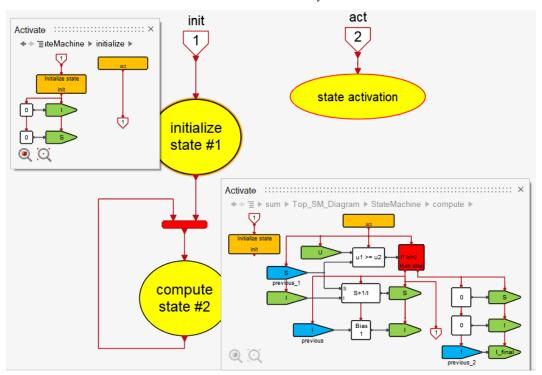

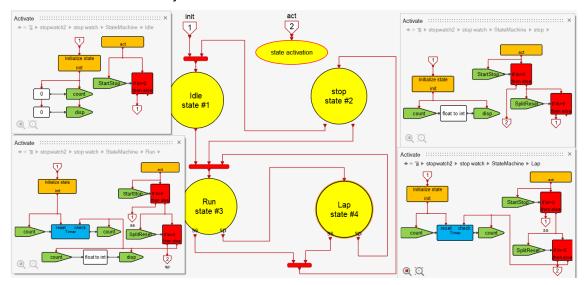

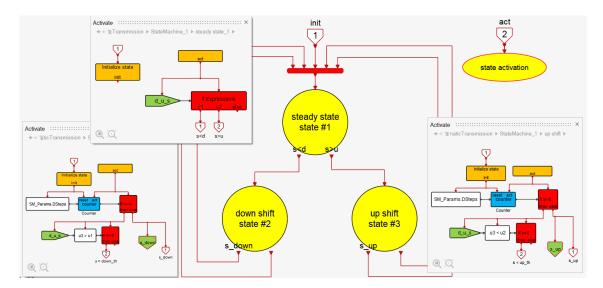

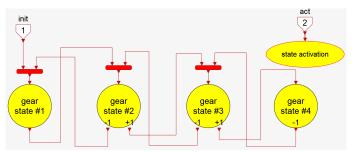

The ASM library provides special blocks for the construction of state machines. These blocks transparently set up the underlying infrastructure required for defining and updating states for State machines. The library can be used to construct machines with hierarchy and parallelism (concurrence). It also provides options such as Run-to-completion and History.

To facilitate the usage of the library, the blocks are designed so that the resulting **Twin Activate** diagram graphically resembles standard state machine diagrams, as it can be seen in specialized tools and languages for constructing state machines. This is done by representing states and state-transitions respectively by (special) Blocks and Activation signals. The definition of state transitions and activations are greatly simplified, and the required constraints are automatically imposed, for example the constraint that two exclusive states should never be active synchronously.

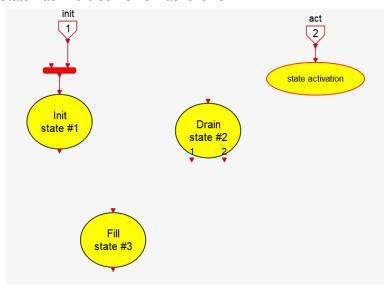

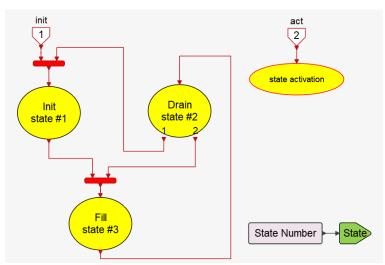

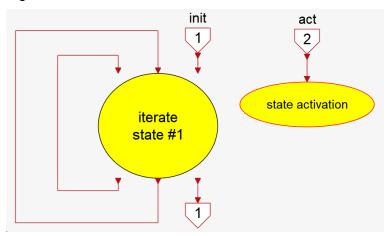

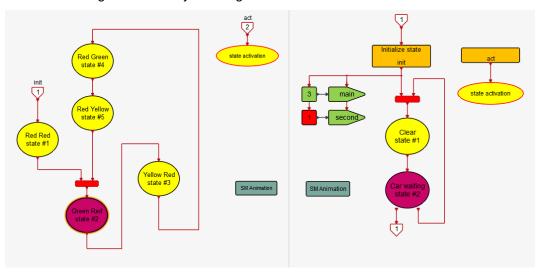

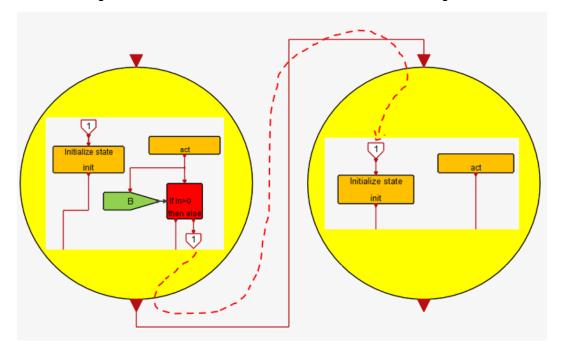

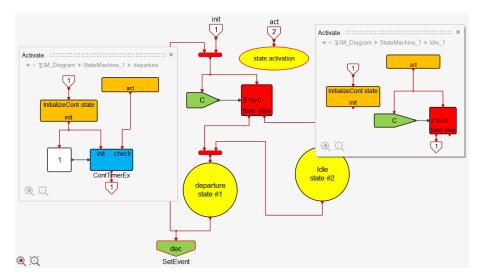

The following diagram shows an implementation of the thermostat example using ASM library blocks

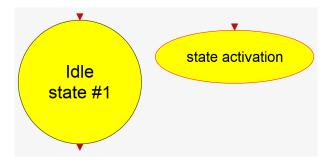

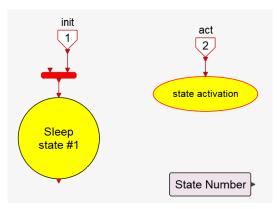

Using the library blocks, user needs not worry about the implementation of the state update mechanism. He/she creates the diagram by placing the state blocks and a state activation block in the diagram (state blocks must be given unique numbers; this constraint is not imposed at construction time, but it is verified by the compiler). The contents of the block states implement their actions.

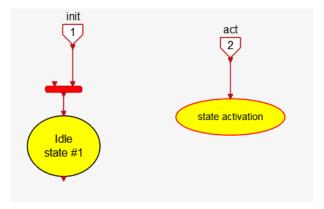

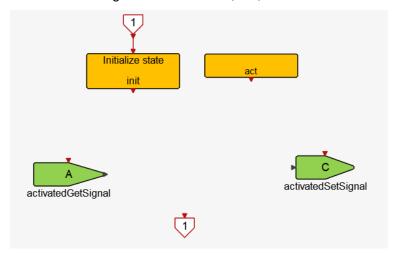

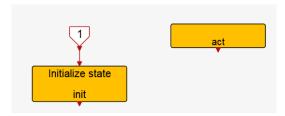

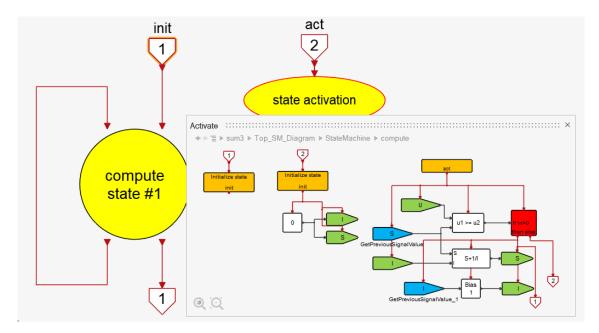

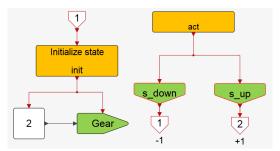

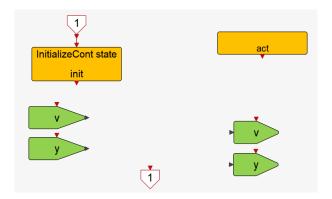

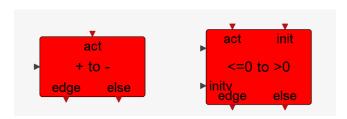

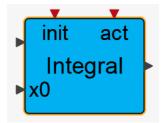

The state blocks come equipped with an **Initialize** block and an **Action** block. The **Initialize** block generates an initialization event, and the **Action** block provides subsequent action events as long as

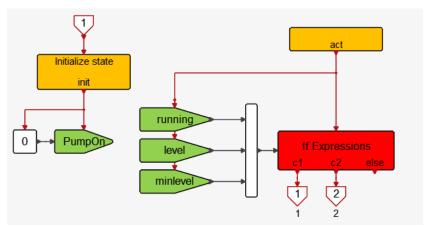

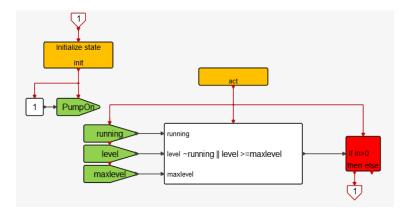

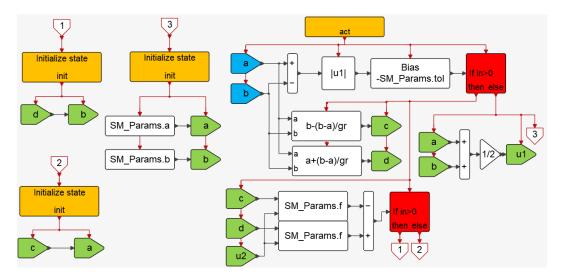

the state block is active. The Off state is for example implemented as follows

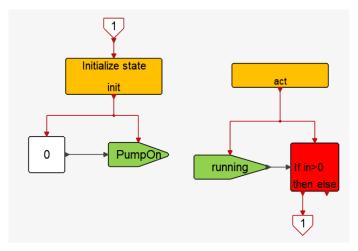

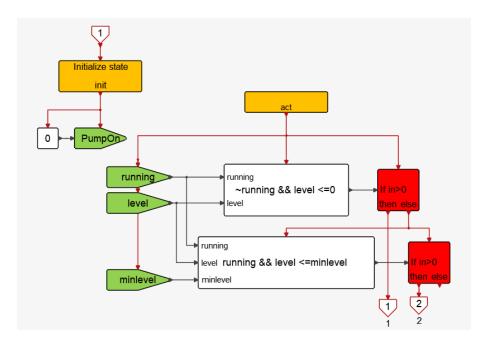

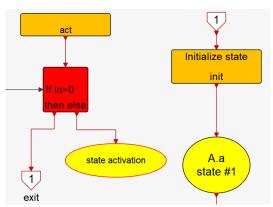

The **Initialize** block receives the event entering the state block, i.e., the event associated with the transition to this block. The initialization event here is used to set the value of the output signal state to 1. After initialization, the act block provides activation signals, which are used to test if the input temperature (Temp signal) has fallen below 17, in which case the event exits the block, initializing the Heat state. The content of the Heat state is shown below

Its operation is straightforward to understand: the state signal is initially set to 2, and subsequently the temperature is tested, leading to an exit if it goes beyond 25.

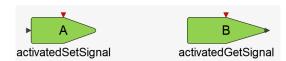

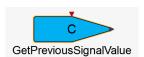

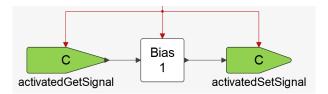

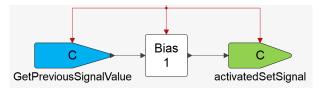

Note the use of activated Set and Get signal blocks to read and write the input temperature and the output state signals. Use of these blocks is not an obligation; state blocks are "normal" super blocks, so regular ports may be added to them. But for simplicity and in particular to keep the diagram visually consistent with state machine diagrams, it is recommended to use activated Set and Get signal blocks and avoid the use of regular links to cross the block state boundaries. Note also that all the blocks inside the state block are explicitly activated. This is not an obligation either; for example, the Bias and the **IfThenElse** blocks would function identically through the inheritance mechanism in the absence of input activation ports. But the use of explicit activation is recommended because it makes the diagram more readable.

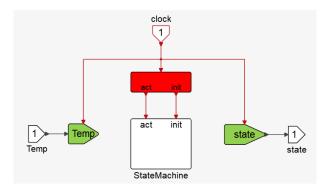

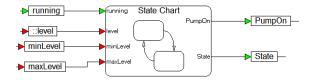

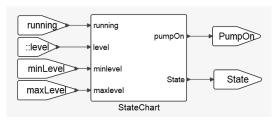

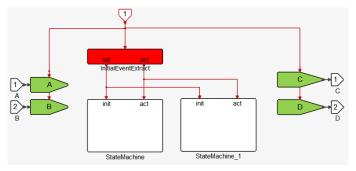

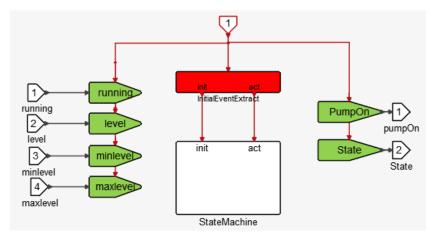

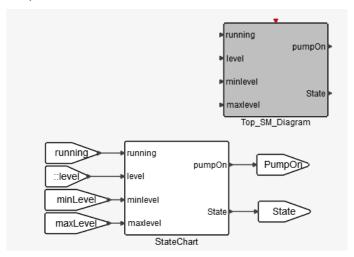

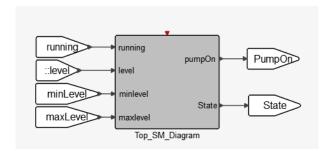

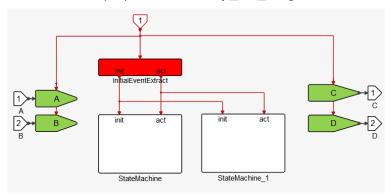

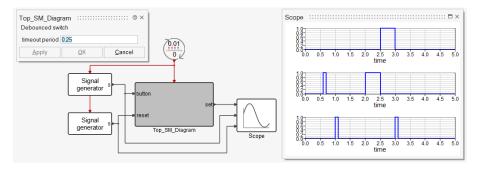

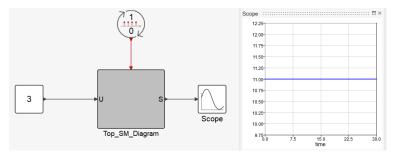

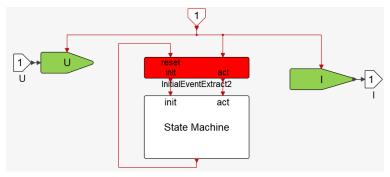

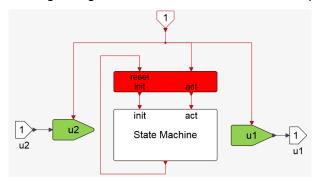

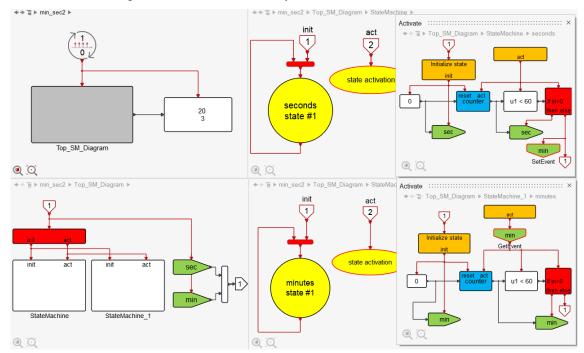

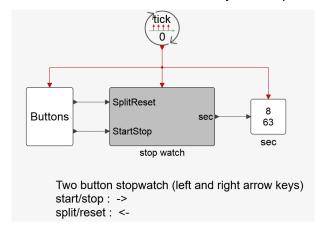

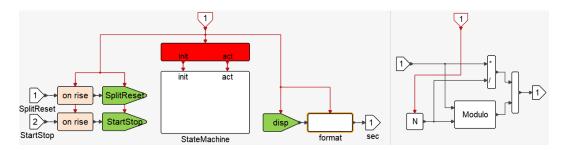

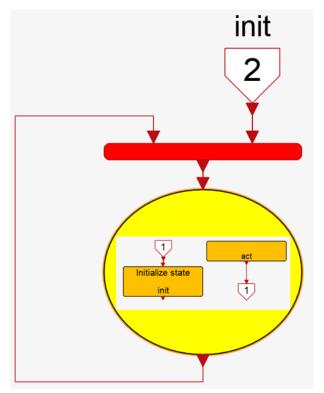

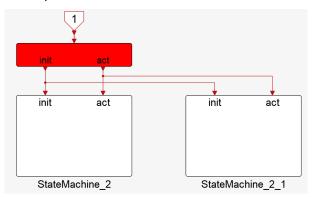

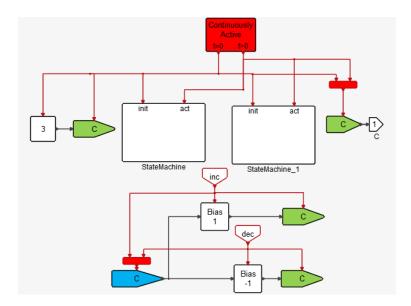

A Thermostat block can then be created by encapsulating the above state machine diagram in the StateMachine super block below

The StateMachine super block layer is not required in this case because the model does not contain parallel state machines. In case it did, the diagram would include multiple StateMachine super blocks, one for each state machine. The systematic use of a super block layer however is useful because it separates the management of the input and outputs from the state machine. In this top diagram, the inputs and outputs are associated with named signals. The activation signal of the block (the clock in most cases), is separated into an initial event (init) and the rest of the events (act). The initial event is used for the initialization of the state machine.

Note that all the user defined blocks in this model are specific to this particular example. The user has not implemented any logic for implementing the state machine mechanism. The mechanism is present inside the library blocks but is not visible, and more importantly, needs not be manipulated by the user.

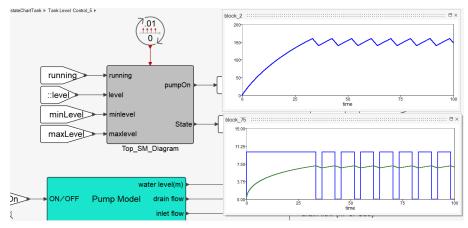

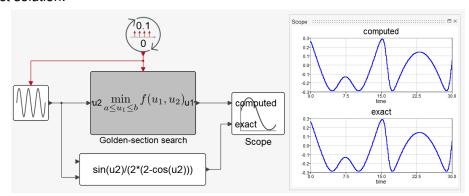

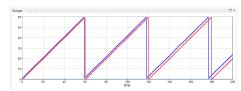

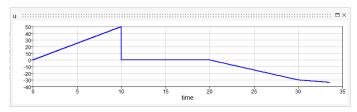

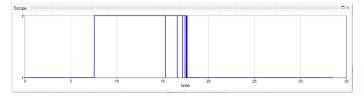

The resulting Thermostat block can now be used as any other block, in an **Twin Activate** model. The following is a simple test model showing its operation.

This example shows the basic idea and methodology behind the **State Machine Library**. It does not show the details of the way the events cause state activations and transitions (in particular the exact timings and the synchronization constraints are not illustrated). These issues are presented and discussed later in this document.

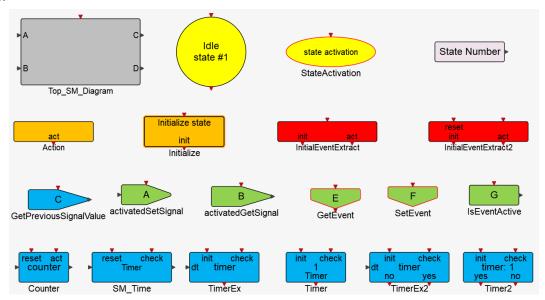

### 2.1 ASM library palette

The ASM library blocks are standard **Twin Activate** blocks or super blocks based on such blocks. Some contain invisible parameters used for the internal state-machine machinery, made transparent to the user, some are programmable super blocks, so with no visible corresponding diagram, but all use only blocks from the Activate Base library. There are no "special" blocks or semantic extensions used behind the scenes. This means that all the functionalities available in **Twin Activate** can be used with models including ASM library blocks. These include model parameterization, code generation, etc.

The ASM library contains blocks specifically developed to be used for the construction of state ma-

chines:

The library includes also utilities blocks for realizing the behavior of various switches and buttons often needed to prepare the input signals to the state machines, in particular signals produced interactively for example through the use of the **Keyboard** block, or imported from data files. The library also includes additional blocks, already available in the Base library, parameterized specifically to be used in the construction of state machines. The sub-palette **ContinuouslyActive** contains blocks dedicated to continuous-time state machines, which will be discussed in Part II.

### 2.2 Steps to create a state machine model using ASM library blocks

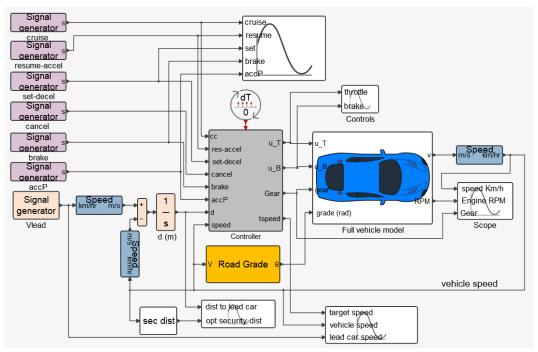

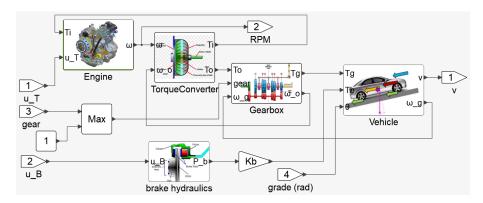

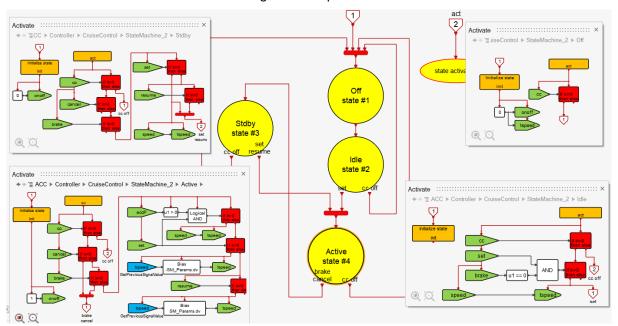

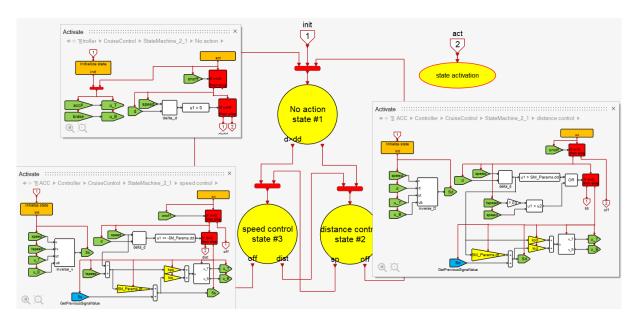

To create a model using state machines, it is important to start by identifying the states of the system. In simple cases (like the simple thermostat above), the state is fully specified by a single state machine. But in general, this is not possible or desirable, and parallel and hierarchical constructions must be envisaged. There are also cases where extended states (non-diagrammed states) must be used.